# Application Note AN-75 LYTSwitch-6 Family

Design Guide

# Introduction

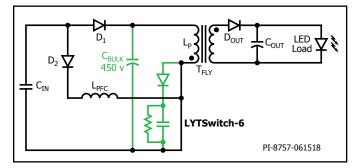

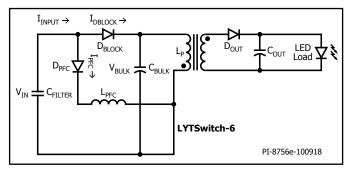

The LYTSwitch<sup>™</sup>-6 series family of ICs dramatically simplifies the development and manufacturing of off-line LED drivers, particularly those in compact enclosures or with high efficiency requirements. The LYTSwitch-6 IC-based architecture is revolutionary, incorporating both primary and secondary controllers, with sense elements and a safety-rated feedback mechanism into a single IC.

Close component proximity and innovative use of the integrated communication link, FluxLink<sup>™</sup>, permits accurate control of a secondary-side synchronous rectification MOSFET and quasi-resonant switching of the primary integrated high-voltage MOSFET. This together with a proprietary adaptive current limit, variable frequency control scheme maintains high efficiency across the entire load range.

The revolutionary control architecture of LYTSwitch-6 IC allows simple implementation of 3-in-1 and DALI dimming. High power factor is also easy to achieve by a passive single-stage Switched Valley-Fill Power Factor Correction (SVFS<sup>2</sup>PFC) circuit.

# Scope

This application note is intended for engineers designing an isolated AC-DC single-stage switched valley-fill power factor correction (SVFS<sup>2</sup>PFC) flyback power supply using the LYTSwitch-6 family of devices. It provides a step-by-step design procedure for the selection of all circuit components.

This application note makes use of the PIXIs Designer, a spreadsheet based application that gives the power supply engineer more control during the design process. The software is part of the PI Expert<sup>™</sup> design software suite which can be downloaded from http://www.power.com/en/design-support/pi-expert-design-software. Online version is also available at http://piexpertonline.power.com.

In addition to this application note the designer may also refer to the many design examples found at www.power.com. They are useful as a starting point for a new design.

# **Quick Start**

Readers familiar with power supply design and Power Integrations design software may elect to skip the step-by-step design approach and use the following information to quickly design the transformer and select the components necessary for a first prototype. For this approach, only the information described below needs to be entered into the PIXIs spreadsheet. Other parameters will be automatically selected based on typical design requirements. References to spreadsheet cell locations are provided in square brackets [cell reference].

- Enter AC input voltage range and line frequency, V<sub>ACMIN</sub> [C3], V<sub>ACNOM</sub> [C4], V<sub>ACMAX</sub> [C5], FL [C6], [C7]

- Enter nominal output voltage, V<sub>o</sub> [C10]

- Enter continuous output current,  $\rm I_{o}$  [C11]

- Select current limit mode, DEVICE\_MODE [C20]

Choose between Standard or Increased

- Select LYTSwitch-6 device from drop down list or enter directly [C21]

- Select the device according to output power and input voltage. (see table 3)

- Enter minimum switching frequency, FS<sub>MIN</sub> [C38]

Choose a value below 50 kHz (optimizes SVFS<sup>2</sup>PFC)

- Enter the PFC inductance to Flyback inductance ratio, RATIO\_LBST\_ LFB [C50]

- Starting value of 0.8 for low-line / wide-range application

- Starting value of 1 for high-line only applications

- Select boost inductor core type, CR\_TYPE\_BOOST [C56]

- Enter the number of boost layers, L\_BOOST [C72]

- Enter desired reflected output voltage,  $V_{_{OR}}$  [C78]

- Select flyback transformer core type, CR\_TYPE [C84]

- Enter the number of primary layers, L [C102]

- Adjust the layers if there is a warning on BOBFILLFACTOR [D94]

- Adjust the layers if there is a warning or info on CMA [D106]

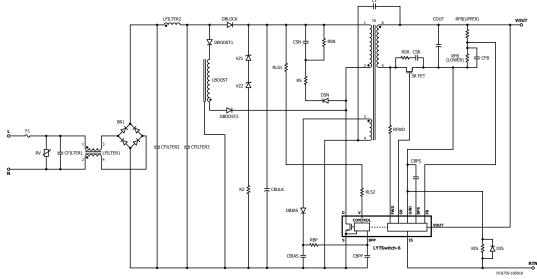

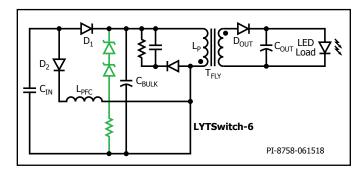

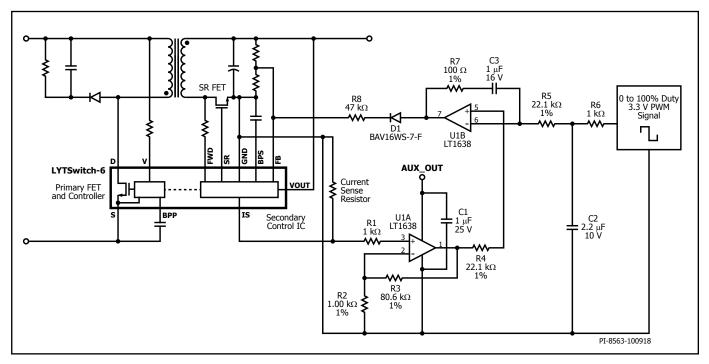

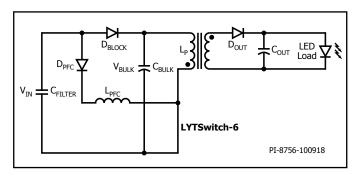

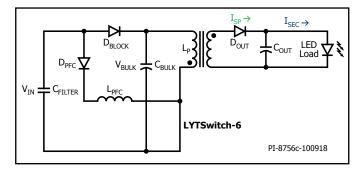

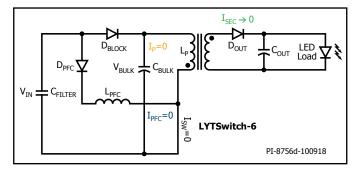

Figure 1. Typical Application Schematic for  $V_{o} < 24$  V.

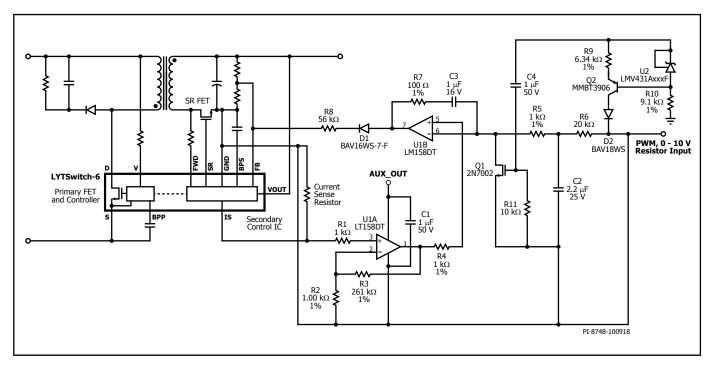

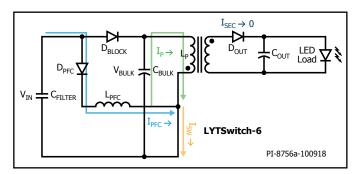

Figure 2. Typical Application Schematic for  $V_{o}$  >24 V.

# **Step-by-Step Design Procedure**

### Step 1 – Application Variables

# Enter: VACMIN, VACNOM, VACMAX, FL, CIN, VO, IO, n, Z

| 1  | ACDC_Flyback_PF_LYTSwitch-<br>6_040618; Rev.1.3; Copyright Power<br>Integrations 2018 | INPUT | INFO | ΟυΤΡυΤ    | UNITS                        | Switched Valley-Fill Single Stage PFC (SVF S^2PFC) |

|----|---------------------------------------------------------------------------------------|-------|------|-----------|------------------------------|----------------------------------------------------|

| 2  | Application Variables                                                                 |       |      |           |                              |                                                    |

| 3  | VACMIN                                                                                |       |      | 90        | V                            | Minimum Input AC Voltage                           |

| 4  | VACNOM                                                                                |       |      | 230       | V                            | Nominal Input AC Voltage                           |

| 5  | VACMAX                                                                                |       |      | 265       | V                            | Maximum Input AC Voltage                           |

| 6  | VACRANGE                                                                              |       |      | UNIVERSAL | -                            | Input Voltage Range                                |

| 7  | FL                                                                                    |       |      | 50        | Hz                           | Line Frequency                                     |

| 8  | CIN                                                                                   |       |      | 60.02     | μF                           | Minimum Input Capacitance                          |

| 9  | V_CIN                                                                                 |       |      | 450       | V                            | Input Capacitance Recommended Voltage Rating       |

| 10 | VO                                                                                    | 40.00 |      | 40.00     | V                            | Output Voltage                                     |

| 11 | Ю                                                                                     | 1.00  |      | 1.00      | A                            | Output Current                                     |

| 12 | PO                                                                                    |       |      | 40.01     | 1 W Total Output Power       |                                                    |

| 13 | N                                                                                     |       |      | 88.00     | 88.00 % Estimated Efficiency |                                                    |

| 14 | Z                                                                                     |       |      | 0.50      | 0.50 Loss Allocation Factor  |                                                    |

Figure 3. Application Variable Section of the Design Spreadsheet.

# Input Voltage and Line Frequency:

$V_{ACMIN}$  (V),  $V_{ACNOM}$  (V),  $V_{ACMAX}$  (V),  $F_{L}$  (Hz) Determine the input voltage range and line frequency from Table 1.

| Region                                                                        | Nominal Input<br>Voltage (VAC) | Minimum Input<br>Voltage (VAC) | Maximum Input<br>Voltage (VAC) | Nominal Line<br>Frequency (Hz) |

|-------------------------------------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|

| Japan                                                                         | 100                            | 85                             | 132                            | 50 / 60                        |

| United States, Canada                                                         | 120                            | 90                             | 132                            | 60                             |

| Australia, China, European Union Countries,<br>India, Korea, Malaysia, Russia | 230                            | 185                            | 265                            | 50                             |

| Indonesia, Thailand, Vietnam                                                  | 220                            | 185                            | 265                            | 50                             |

|                                                                               | 115, 120, 127                  | 90                             | 155                            | 50 / 60                        |

| Rest of Europe, Asia, Africa, Americas<br>and rest of the world               | 220, 230                       | 185                            | 265                            | 50 / 60                        |

|                                                                               | 240                            | 185                            | 265                            | 50                             |

Table 1. Input Line Voltage Ranges and Line Frequencies.

Use table 2 as guidance for selecting the bulk capacitance. The recommended voltage rating is given by V\_CIN.

| Input Voltage<br>(VAC) | Input Bulk Capacitance per<br>Watt Output Power (μF/W) |

|------------------------|--------------------------------------------------------|

| 100 / 115              | 1 to 1.5                                               |

| 230                    | 0.5 to 1                                               |

| 85 - 265               | 1 to 1.5                                               |

Table 2. Recommended Bulk Capacitance.

#### Nominal Output Voltage, VO (V)

Enter the nominal output voltage of the main output in the constant voltage operating region. This value is recommended to be at least 3 V higher than the maximum LED voltage.

#### Output Current, I<sub>o</sub> (A)

Enter the maximum continuous LED load current.

#### Output Power, PO (W)

This is a calculated value based on the output voltage and current.

#### Estimated Efficiency, n

The default value is 88%. Once the prototype is completed, update value with the measured efficiency and fine tune the components.

#### Loss Allocation Factor, Z

This factor represents the proportion of losses in the primary and in the secondary of the power supply. Z factor is used together with efficiency to determine the actual power that must be delivered by the power stage. For example, losses in the input stage (EMI filter, rectification, etc.) are not processed by the power stage (transferred through the transformer). Although they reduce efficiency, the transformer design is not effected by these losses.

For designs that do not have peak power requirement, a value of 0.5 is recommended. For designs with a peak power requirement enter 0.65. A higher number indicates a larger proportion of secondary-side losses.

$$Z = \frac{\text{Secondary Losses}}{\text{Total Losses}}$$

## Step 2 – Parametric Calculation Basis

#### Select: PARcalcBASIS, Flyback\_Ind\_Basis, Boost\_Ind\_Basis

| 1  | ACDC_Flyback_PF_LYTSwitch-<br>6_040618; Rev.1.3; Copyright Power<br>Integrations 2018 | INPUT      | INFO | OUTPUT     | UNITS | Switched Valley-Fill Single Stage PFC (SVF<br>S^2PFC)                                               |

|----|---------------------------------------------------------------------------------------|------------|------|------------|-------|-----------------------------------------------------------------------------------------------------|

| 15 | Calculations Basis                                                                    |            |      |            |       |                                                                                                     |

| 16 | PARcalcBASIS                                                                          | Worst_Case |      | Worst_Case |       | Calculated Results Based on Selected VAC -<br>VACNOM,VACMAX,VACMIN or Worst Case only               |

| 17 | Flyback_Ind_Basis                                                                     | Nom        |      | Nom        |       | Calculated Results Based on Selected LP - Min<br>= LP_MIN, Nom = LP_NOM, Max = LP_MAX               |

| 18 | Boost_Ind_Basis                                                                       | Nom        |      | Nom        |       | Calculated Results Based on Selected LBOOST -<br>Min = LBOOSTMIN,Nom = LBOOSTNOM,Max =<br>LBOOSTMAX |

Figure 4. Parametric Calculation Basis Section of the Design Spreadsheet.

| 1  | ACDC_Flyback_PF_LYTSwitch-<br>6_040618; Rev.1.3; Copyright Power<br>Integrations 2018 | INPUT | INFO | Ουτρυτ  | UNITS | Switched Valley-Fill Single Stage PFC (SVF<br>S^2PFC) |

|----|---------------------------------------------------------------------------------------|-------|------|---------|-------|-------------------------------------------------------|

|    | Calculated Electrical Parameters Based                                                |       |      |         |       |                                                       |

| 30 | on Specified Basis                                                                    |       |      |         |       |                                                       |

| 31 | Boost Converter                                                                       |       |      |         |       |                                                       |

| 32 | IBOOSTRMS                                                                             |       |      | 439.72  | mA    | Boost RMS current                                     |

| 33 | IBOOSTMAX                                                                             |       |      | 1092.16 | mA    | Boost PEAK current                                    |

| 34 | IBOOSTAVG                                                                             |       |      | 313.88  | mA    | Boost AVG current                                     |

| 35 | IINRMS                                                                                |       |      | 673.27  | mA    | Input RMS current                                     |

| 36 | PF_est                                                                                |       |      | 0.7524  |       | Estimated Power Factor                                |

Figure 5. Calculated Electrical Parameters Section of the Design Spreadsheet.

#### Parametric Calculation Basis, PARcalcBASIS

This parameter provides information about the converter electrical parameters at a set input voltage. This affects the values of boost current, FET current, flyback transformer current (RMS, max, average), as well as the estimated power factor and  $K_{\rm p}$ .

The selection of 'Worst\_Case' is recommended in order to confirm that critical parameters like  $K_{\rm p}$  and  $FS_{\rm MAX}$  are within acceptable limits under worst-case conditions.

#### Flyback Inductance Basis, Flyback\_Ind\_Basis

Select the flyback inductance tolerance that will be used in the calculation. It is set to nominal (Nom) by default.

#### Boost Inductance Basis, Boost\_Ind\_Basis

Select the boost inductance tolerance that will be used in the calculation. It is set to nominal (Nom) by default.

#### PF Estimate, PF\_est

The estimated power factor, PF\_est, might appear low if the calculation is made at the worst-case input voltage and component tolerances. Unless PF needs to be guaranteed at the minimum input voltage, it is recommended to perform the calculation using VACNOM when estimating for power factor and verify actual values during prototype testing.

# Step 3 – Primary Controller Section

#### Enter: Device Name, Current Limit Mode, Breakdown Voltage

| 1  | ACDC_Flyback_PF_LYTSwitch-<br>6_040618; Rev.1.3; Copyright Power<br>Integrations 2018 | INPUT     | INFO | OUTPUT    | UNITS | Switched Valley-Fill Single Stage PFC (SVF<br>S^2PFC)          |

|----|---------------------------------------------------------------------------------------|-----------|------|-----------|-------|----------------------------------------------------------------|

| 19 | Primary Controller Section                                                            |           |      |           |       |                                                                |

| 20 | DEVICE_MODE                                                                           | Increased |      | Increased |       | Device Current Limit Mode                                      |

| 21 | DEVNAME                                                                               | LYT6068C  |      | LYT6068C  |       | PI Device Name                                                 |

| 22 | RDSON                                                                                 |           |      | 1.53      | Ohm   | Device RDSON at 100degC                                        |

| 23 | ILIMITMIN                                                                             |           |      | 1.683     | A     | Minimum Current Limit                                          |

| 24 | ILIMITTYP                                                                             |           |      | 1.850     | A     | Typical Current Limit                                          |

| 25 | ILIMITMAX                                                                             |           |      | 2.017     | A     | Maximum Current Limit                                          |

| 26 | POUT_MAX                                                                              |           |      | 55.000    | w     | Power Capability of the Device based on Thermal<br>Performance |

| 27 | BVDSS                                                                                 | Auto      |      | 650       | V     | Peak Drain to Source Breakdown Voltage                         |

| 28 | VDS                                                                                   |           |      | 2.00      | V     | On state Drain to Source Voltage                               |

| 29 | VDRAIN                                                                                |           |      | 544.77    | V     | Peak Drain to Source Voltage during Fet turn off               |

Figure 6. Parametric Calculation Basis Section of the Design Spreadsheet.

#### Device Current Limit Mode, DEVICE\_MODE

The device has two current limit options – STANDARD or INCREASED. By default, DEVICE\_MODE is set to STANDARD. For designs where lowest cost is a critical requirement, choose INCREASED current limit mode to enable the same device to operate at higher power. Ensure that thermal performance is acceptable.

#### Device Code, DEVNAME

The power table on LYTSwitch-6 data sheet is based on a non-PF configuration. With the addition of SVFS<sup>2</sup>PFC circuit, a 20% power derating is recommended when choosing the LYTSwitch-6 device for best efficiency and for optimizing thermal management.

# Breakdown Voltage Selection, $BV_{DSS}$ (V)

LYTSwitch-6 ICs are available with 650 V or 725 V primary switch options. For example, LYT6063C describes a 650 V MOSFET device and LYT6073C denotes 725 V.

This option is applicable only when the device code  $\mathsf{DEVNAME}$  is set to AUTO.

| Product          | 277 VAC ±<br>15% | 380 VDC /<br>450 VDC                       |      |  |

|------------------|------------------|--------------------------------------------|------|--|

| Floader          |                  | mended Power<br>With SVFS <sup>2</sup> PFC |      |  |

| LYT6063C / 6073C | 12 W             | 9.6 W                                      | 20 W |  |

| LYT6065C / 6075C | 24 W             | 20 W                                       | 32 W |  |

| LYT6067C / 6077C | 40 W             | 36 W                                       | 48 W |  |

| LYT6068C         | 55 W             | 45 W                                       |      |  |

Table 3.

Device Selection Based on Operating with an SVFS<sup>2</sup>PFC Stage.

# Step 4 – Enter Minimum Switching Frequency

| 1  | ACDC_Flyback_PF_LYTSwitch-<br>6_040618; Rev.1.3; Copyright Power<br>Integrations 2018 | INPUT | INFO | OUTPUT    | UNITS | Switched Valley-Fill Single Stage PFC (SVF<br>S^2PFC)            |

|----|---------------------------------------------------------------------------------------|-------|------|-----------|-------|------------------------------------------------------------------|

| 37 | Flyback Converter                                                                     |       |      |           |       |                                                                  |

| 38 | FSMIN                                                                                 | 45000 |      | 45000     | Hz    | Minimum Switching Frequency in a Line Period                     |

| 39 | FSMAX                                                                                 |       |      | 108744.24 | Hz    | Maximum Switching Frequency in a Line Period                     |

| 40 | KPmin                                                                                 |       |      | 0.5187    |       | Minimum KP in a Line Period for VAC specified<br>by PARcalcBASIS |

| 41 | IFETRMS                                                                               |       |      | 803.16    | mA    | Fet RMS current                                                  |

| 42 | IFETMAX                                                                               |       |      | 1864.84   | mA    | Fet PEAK current                                                 |

| 43 | IPRIRMS                                                                               |       |      | 0.6058    | A     | Primary Winding RMS current                                      |

| 44 | IPRIMAX                                                                               |       |      | 1.6647    | A     | Primary Winding PEAK current                                     |

| 45 | IPRIAVG                                                                               |       |      | 0.2479    | A     | Primary Winding AVG current                                      |

| 46 | IPRIMIN                                                                               |       |      | 929.59    | mA    | Primary Winding Minimum current                                  |

| 47 | ISECRMS                                                                               |       |      | 1.69      | A     | Secondary RMS current                                            |

| 48 | ISECMAX                                                                               |       |      | 4.31      | A     | Secondary PEAK current                                           |

Figure 7. Flyback Converter Section of the Design Spreadsheet.

#### Minimum Switching Frequency, FSMIN (Hz)

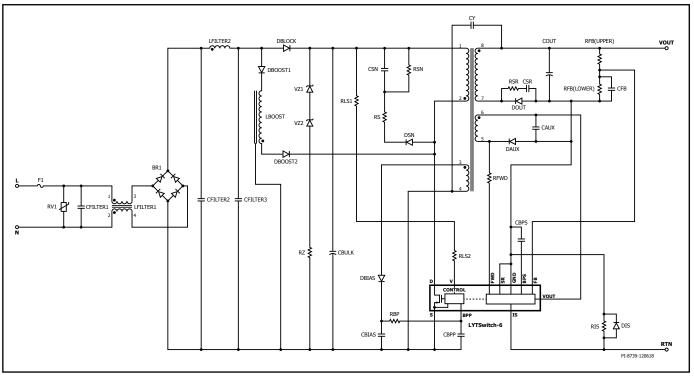

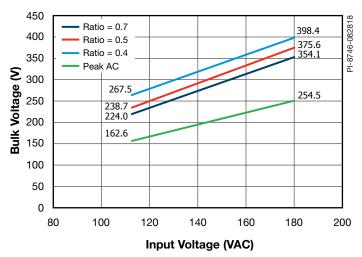

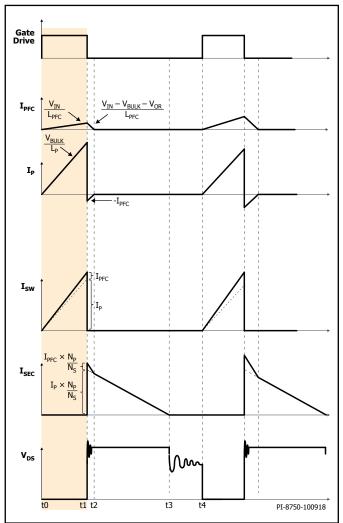

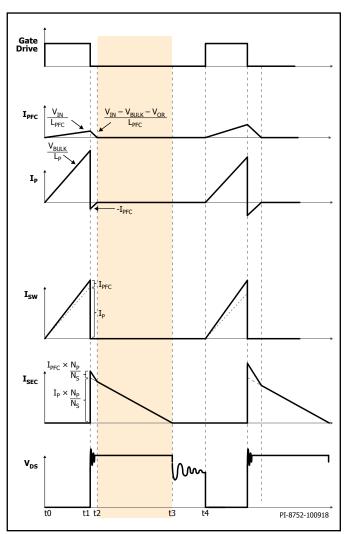

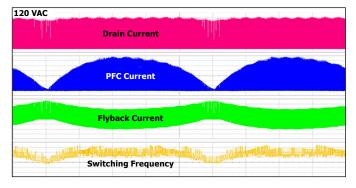

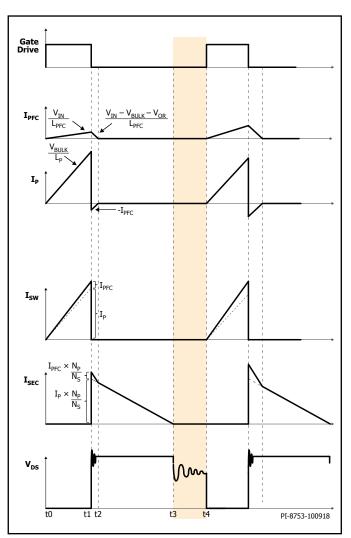

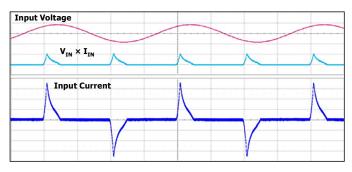

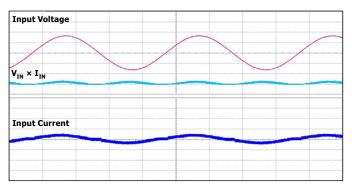

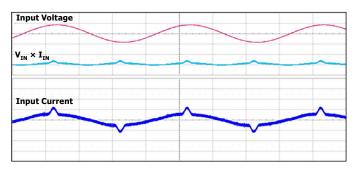

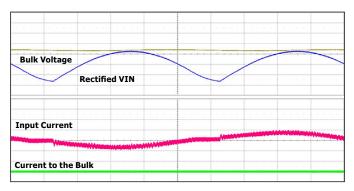

Figure 8 shows the typical LYTSwitch-6 + SVFS<sup>2</sup>PFC switching profile. The minimum frequency occurs at the zero-crossing and increases with line. It resembles an M-shape in a ½ line cycle. It is recommended to set FSMIN below 50 kHz to minimize switching losses. Adjust FSMIN if there is a warning flag on FSMAX.

#### Maximum Switching Frequency, FSMAX (Hz)

This parameter is the calculated maximum operating frequency based on the chosen FSMIN and parametric calculations. Ideally, FSMAX should be <100 kHz to minimize switching losses. Higher frequency is permitted but regulation, efficiency, and thermal performance should be verified via bench testing.

Figure 8. LYTSwitch-6 + SVFS<sup>2</sup>PFC Switching Profile (Simulated).

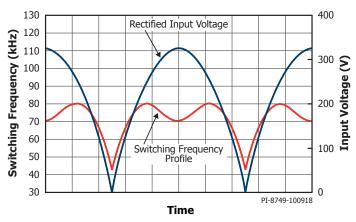

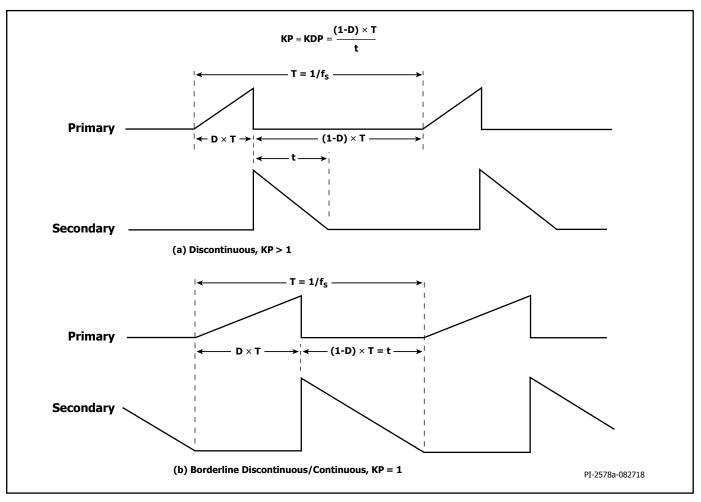

#### Mode of Operation, KP

KP is a measure of how discontinuous or continuous switching is. KP > 1 denotes discontinuous conduction mode (DCM), while KP <1 corresponds to continuous conduction mode (CCM).

#### KP < 1

In continuous conduction mode (CCM), KP is defined as the ratio of ripple current to the primary peak current.

$$KP \equiv KRP = \frac{I_R}{I_P}$$

Figure 9. Continuous Conduction Mode Current Waveform, KP < 1.

# KP > 1

If the KP >1, it indicates that the converter is operating in discontinuous conduction mode (DCM). In this case, KP is defined as the ratio of the primary MOSFET off time to the secondary rectifier conduction time.

$$KP \equiv KDP = \frac{(1-D) \times T}{t}$$

$$= \frac{V_{OR} \times (1-D_{MAX})}{(V_{MIN} - V_{DS}) \times D_{MAX}}$$

#### **Minimum KP, KPMIN**

KPMIN provides information on minimum operating KP based on the selected parameters.

A value of >1 is ideal and usually results in highest efficiency. However, for a universal input, high-power design, KP <1 may be unavoidable. Verify  $KP_{MIN}$  at worst-case condition and target  $KP_{MIN}$  to be above 0.5. The more continuous operation becomes, the more likely that the PFC inductor will operate in CCM. The PFC inductor needs to operate in DCM for proper operation so if KPMIN is too low, this will force the boost-inductance-to-flyback-inductance ratio (RATIO\_LBST\_LFB) to also be lower, which could degrade the efficiency.

- Use larger device

- Increase V<sub>OR</sub>

- Increase bulk capacitance

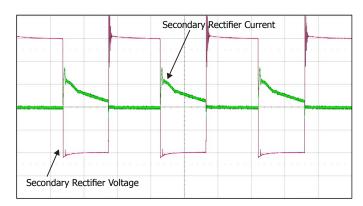

Figure 10. Discontinuous Conduction Mode Current Waveform,  $K_p > 1$ .

# Step 5 – PFC (Boost) Parameters

# Enter: RATIO\_LBST\_LFB, LBOOSTTOL

| 1  | ACDC_Flyback_PF_LYTSwitch-<br>6_040618; Rev.1.3; Copyright Power<br>Integrations 2018 | INPUT | INFO OUT |        | UNITS | Switched Valley-Fill Single Stage PFC (SVF<br>S^2PFC)    |

|----|---------------------------------------------------------------------------------------|-------|----------|--------|-------|----------------------------------------------------------|

| 49 | Boost Choke Construction Parameters                                                   |       |          |        |       |                                                          |

| 50 | RATIO_LBST_LFB                                                                        | 0.8   |          | 0.8000 |       | Boost Inductance and Flyback Primary<br>Inductance Ratio |

| 51 | LBOOSTMIN                                                                             |       |          | 512.07 | μH    | Minimum Boost Inductance                                 |

| 52 | LBOOSTNOM                                                                             |       |          | 568.96 | μH    | Nominal Boost Inductance                                 |

| 53 | LBOOSTMAX                                                                             |       |          | 625.86 | μH    | Maximum Boost Inductance                                 |

| 54 | LBOOSTTOL                                                                             |       |          | 10.00  | %     | Boost Inductance Tolerance                               |

Figure 11. PFC (Boost) Inductor Section of the Design Spreadsheet.

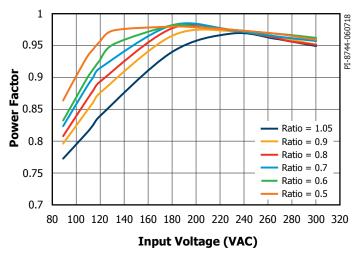

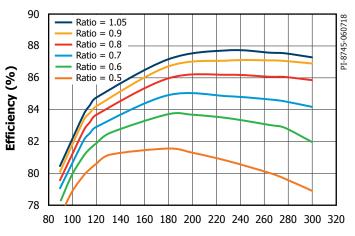

#### Boost Inductance to Flyback Primary Inductance Ratio, RATIO\_LBST\_LFB

The selected FSMIN determines the required flyback primary inductance. The PFC (boost) inductance is determined by the value in the RATIO\_LBST\_LFB cell, the ratio between the boost inductance (LBOOST\_NOM) and the flyback inductance (LP\_NOM).

$$RATIO\_LBST\_LFB = \frac{LBOOSTNOM}{LPNOM}$$

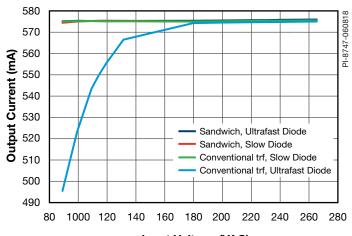

The default value for low-line/universal input is 0.8. For high-line, the default value is 1. A lower ratio increases the PF (Figure 12), but degrades efficiency (Figure 13). Table 4 summarizes the benefits and disadvantages selecting a lower ratio.

Figure 12. Power Factor vs. RATIO\_LBST\_LFB.

#### Input Voltage (VAC)

Figure 13. Efficiency vs. RATIO\_LBST\_LFB.

#### Effect of Lower RATIO\_LBST\_LFB Value on Various Parameters

| Parameter                                | Impact |

|------------------------------------------|--------|

| Power Factor                             | Higher |

| Efficiency                               | Lower  |

| A-THD                                    | Lower  |

| No-Load Input Power                      | Higher |

| No-Load Bulk Voltage                     | Higher |

| Maximum Operating<br>Switching Frequency | Higher |

Table 4. Effect of Lower RATIO\_LBST\_LFB on Various Parameters.

#### Nominal Boost Inductance, LBOOST\_NOM

This is the target value for the typical boost inductance. This value is dependent on RATIO\_LBST\_LFB and the flyback inductance. The boost inductor should operate in discontinuous conduction mode (DCM).

#### Boost Inductance Tolerance, LBOOST\_TOL

This parameter is the assumed tolerance for boost inductance. A value of 10% is used by default, a different value may be entered in the grey override cell. A value of 10% is easy to meet for most magnetics vendors, but a lower value will help increase production tolerance.

# Step 6 – Boost Inductor Design

Enter: Boost Parameters (AE, LE, AL, VE, AW, BW, NBOOST, L\_BOOST, AWG\_BOOST)

| 1  | ACDC_Flyback_PF_LYTSwitch-<br>6_040618; Rev.1.3; Copyright Power<br>Integrations 2018 | INPUT | INFO | ΟυΤΡυΤ         | UNITS           | Switched Valley-Fill Single Stage PFC (SVF<br>S^2PFC)    |

|----|---------------------------------------------------------------------------------------|-------|------|----------------|-----------------|----------------------------------------------------------|

| 56 | CR_TYPE_BOOST                                                                         | Auto  |      | EE13           |                 | Boost Core                                               |

| 57 | CR_PN_BOOST                                                                           |       |      | PC40EE13-<br>Z |                 | Boost Core Code                                          |

| 58 | AE_BOOST                                                                              |       |      | 17.10          | mm^2            | Boost Core Cross Sectional Area                          |

| 59 | LE_BOOST                                                                              |       |      | 30.20          | mm              | Boost Core Magnetic Path Length                          |

| 60 | AL_BOOST                                                                              |       |      | 1130.00        | nH/turns^2      | Boost Core Ungapped Core Effective Inductance            |

| 61 | VE_BOOST                                                                              |       |      | 517.00         | mm^3            | Boost Core Volume                                        |

| 62 | BOBBINID_BOOST                                                                        |       |      | 548            |                 | Bobbin                                                   |

| 63 | AW_BOOST                                                                              |       |      | 22.20          | mm^2            | Window Area of Bobbin                                    |

| 64 | BW_BOOST                                                                              |       |      | 7.40           | mm              | Bobbin Width                                             |

| 65 | MARGIN_BOOST                                                                          |       |      | 0.00           | mm              | Safety Margin Width                                      |

| 66 | BOBFILLFACTOR_Boost                                                                   |       |      | 84.21          | %               | Boost Bobbin Fill Factor                                 |

| 67 | Boost Winding Details                                                                 |       |      |                |                 |                                                          |

| 68 | NBOOST                                                                                |       |      | 107.00         |                 | Boost Choke Turns                                        |

| 69 | BP_BOOST                                                                              |       |      | 3735.79        | Gauss           | Boost Peak Flux Density                                  |

| 70 | ALG_BOOST                                                                             |       |      | 49.70          | nH/turns^2      | Boost Core Ungapped Core Effective Inductance            |

| 71 | LG_BOOST                                                                              |       |      | 0.41           | mm              | Boost Core Gap Length                                    |

| 72 | L_BOOST                                                                               |       |      | 6.50           |                 | Number of Boost Layers                                   |

| 73 | AWG_BOOST                                                                             |       |      | 27             |                 | Boost Winding Wire AWG                                   |

| 74 | OD_BOOST_INSULATED                                                                    |       |      | 0.418          | mm              | Boost Winding Wire Output Diameter with<br>Insulation    |

| 75 | OD_BOOST_BARE                                                                         |       |      | 0.361          | mm              | Boost Winding Wire Output Diameter without<br>Insulation |

| 76 | CMA_BOOST                                                                             |       |      | 471.92         | Circular Mils/A | Boost Winding Wire CMA                                   |

Figure 14. Boost Inductor Construction Section of the Design Spreadsheet.

#### Boost Inductor Core Type, CR\_TYPE\_BOOST

By default, the spreadsheet will select the smallest commonly available core suitable for the specified output power. Different core types and sizes from the drop down list are available and if the user-preferred core is not available, the grey override cells (AE\_BOOST, LE\_BOOST, AL\_BOOST, VE\_BOOST, AW\_BOOST and BW\_BOOST) can be used to enter the core and bobbin parameters directly.

Table 5 provides core selection guidelines based on output power. Off-the-shelf drum-type inductors may be used, but a shielded type is recommended to minimize EMI emission.

#### **Boost Inductor Turns, NBOOST**

This is the number of turns for the boost winding calculated based on required boost inductance.

#### Boost Layers, L\_BOOST; Boost Winding Wire Gauge, AWG\_BOOST

Either boost layers L\_BOOST or AWG\_BOOST can be set by the user in order to optimize the bobbin fill BOBFILLFACTOR\_Boost and winding current capacity CMA\_BOOST a value between 200 and 500 Cmil/A is recommended.

|                    |          | Core and Bobbin Table |       |        |         |       |           |       |      |  |  |  |  |

|--------------------|----------|-----------------------|-------|--------|---------|-------|-----------|-------|------|--|--|--|--|

|                    |          |                       |       | Bobbin |         |       |           |       |      |  |  |  |  |

| Output             | <b>6</b> | Code                  | AE    | LE     | AL      | VE    | Code      | AW    | BW   |  |  |  |  |

| Power at<br>75 kHz | Core     |                       | (mm²) | (mm)   | (nH/T²) | (mm³) | Coue      | (mm²) | (mm) |  |  |  |  |

| < 15 W             | EE8.3    | B-EE8-H               | 7.0   | 19.2   | 610     | 154   | B-EE8.3-H | 6.96  | 4.78 |  |  |  |  |

| 15 W – 30 W        | EE10     | PC47EE10-Z            | 12.1  | 26.1   | 850     | 300   | B-EE10-H  | 12.21 | 6.60 |  |  |  |  |

| 30 W – 45 W        | EE13     | PC47EE13-Z            | 17.1  | 30.2   | 1130    | 517   | B-EE13-H  | 18.43 | 7.60 |  |  |  |  |

| > 45 W             | EE16     | PC47EE16-Z            | 19.2  | 35.0   | 1140    | 795   | B-EE16-H  | 14.76 | 8.50 |  |  |  |  |

Table 5. Commonly Available Cores and Power Levels at Which These Cores can be used for Typical Boost Inductor Design.

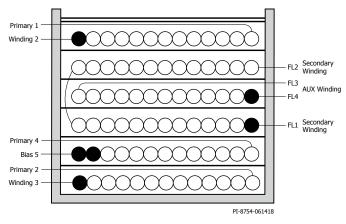

# Step 7 – Design the Flyback Transformer

### Enter: VOR, Core Parameters, L, AWG, NS

| 6_     | CDC_Flyback_PF_LYTSwitch-<br>_040618; Rev.1.3; Copyright Power<br>tegrations 2018 | INPUT   | INFO | OUTPUT                | UNITS                  | Switched Valley-Fill Single Stage PFC (SVF<br>S^2PFC)        |

|--------|-----------------------------------------------------------------------------------|---------|------|-----------------------|------------------------|--------------------------------------------------------------|

|        | lyback Transformer Construction                                                   | INFOT   | INFO | 001701                | 01113                  | S <sup>-</sup> ZFFC)                                         |

|        | arameters                                                                         |         |      |                       |                        |                                                              |

| 78 V   | OR                                                                                | 100.00  |      | 100.00                | v                      | Secondary Voltage Reflected in the Primary<br>Winding        |

| 79 LF  | P_MIN                                                                             |         |      | 640.08                | μH                     | Minimum Flyback Inductance                                   |

| 80 LF  | P_NOM                                                                             |         |      | 711.20                | μH                     | Nominal Flyback Inductance                                   |

| 81 LF  | P_MAX                                                                             |         |      | 782.33                | μH                     | Maximum Flyback Inductance                                   |

| 82 LF  | P_TOL                                                                             |         |      | 10.00                 | %                      | Flyback Inductance Tolerance                                 |

| 83 FI  | yback Core and Bobbin Selection                                                   |         |      |                       |                        |                                                              |

| 84 C   | R_TYPE                                                                            | PQ26/20 |      | PQ26/20               |                        | Flyback Core                                                 |

| 85 C   | R_PN                                                                              |         |      | PQ26/20-<br>3F3       |                        | Flyback Core Code                                            |

| 86 A   | E                                                                                 |         |      | 121.00                | mm^2                   | Flyback Core Cross Sectional Area                            |

| 87 LE  | E                                                                                 |         |      | 45.00                 | mm                     | Flyback Core Magnetic Path Length                            |

| 88 AI  | L                                                                                 |         |      | 5200.00               | nH/turns^2             | Flyback Core Ungapped Core Effective Inductance              |

| 89 V   |                                                                                   |         |      | 5470.00               | mm^3                   | Flyback Core Volume                                          |

|        | OBBINID                                                                           |         |      | BPQ26/20-<br>1112CPFR |                        | Flyback Bobbin                                               |

| 91 A'  | W                                                                                 |         |      | 31.10                 | mm^2                   | Flyback Window Area of Bobbin                                |

| 92 B'  | W                                                                                 |         |      | 9.00                  | mm                     | Flyback Bobbin Width                                         |

| 93 M   | ARGIN                                                                             |         |      | 0.00                  | mm                     | Safety Margin Width                                          |

| 94 B   | OBFILLFACTOR                                                                      |         |      | 58.69                 | %                      | Flyback Bobbin Fill Factor                                   |

| 95 FI  | yback Winding Details                                                             |         |      |                       |                        |                                                              |

| 96 N   |                                                                                   |         |      | 37.00                 |                        | Primary Turns                                                |

| 97 B   | P                                                                                 |         |      | 3630.38               | Gauss                  | Flyback Peak Flux Density                                    |

| 98 BI  | M                                                                                 |         |      | 3484.88               | Gauss                  | Flyback Maximum Flux Density                                 |

| 99 B.  | AC                                                                                |         |      | 1408.39               | Gauss                  | Flyback AC Flux Density                                      |

| 100 A  | LG                                                                                |         |      | 519.51                | nH/turns^2             | Flyback Core Ungapped Core Effective Inductance              |

| 101 L0 | 3                                                                                 |         |      | 0.26                  | mm                     | Flyback Core Gap Length                                      |

| 102 L  |                                                                                   |         |      | 2.00                  |                        | Number of Flyback Layers                                     |

| 103 A  | WG                                                                                |         |      | 26                    |                        | Primary Winding Wire AWG                                     |

| 104 O  | D                                                                                 |         |      | 0.465                 | mm                     | Primary Winding Wire Output Diameter with Insulation         |

| 105 D  | IA                                                                                |         |      | 0.405                 | mm                     | Primary Winding Wire Output Diameter without<br>Insulation   |

| 106 C  | MA                                                                                |         |      | 467.83                | Circular Mils/A        | Primary Winding Wire CMA                                     |

| 107 N  | В                                                                                 |         |      | 5.00                  |                        | Bias Turns                                                   |

| 108 A  | WGpBias                                                                           |         |      | 32                    |                        | Bias Wire AWG                                                |

| 109 N  | S                                                                                 |         |      | 15.00                 |                        | Secondary Turns                                              |

| 110 A' | WGS                                                                               |         |      | 25                    |                        | Secondary Winding Wire AWG                                   |

| 111    | DC                                                                                |         |      | 0.760                 |                        | Secondary Winding Wire Output Diameter with                  |

|        | DS                                                                                |         |      | 0.760                 | mm                     | Insulation<br>Secondary Winding Wire Output Diameter without |

|        | IAS                                                                               |         |      | 0.455                 | mm<br>Circular Mile (A | Insulation                                                   |

| 113 C  | MAS                                                                               |         |      | 200.71                | Circular Mils/A        | Secondary Winding Wire CMA                                   |

Figure 15. Flyback Transformer Construction Section of the Design Spreadsheet.

## **Reflected Output Voltage, VOR**

This parameter is the voltage seen across the secondary winding during the diode / synchronous rectifier MOSFET (SR FET) conduction-time, reflected back to the primary through the turns ratio of the transformer. VOR can be adjusted to limit Drain-Source voltage of the primary-side MOSFET. VOR should be adjusted to eliminate warnings on the spreadsheet. For design optimization purposes, the following should be considered:

- Higher VOR reduces voltage stress on the output diodes and SR MOSFETs. In some cases this may allow a lower voltage rating and higher efficiency.

- Higher VOR increases leakage inductance which reduces power supply efficiency.

- Higher VOR increases secondary-side peak and RMS current which may increase secondary-side copper, diode and SR MOSFET losses and reduce efficiency.

- Higher VOR makes the KP higher (more Discontinuous or less Continuous) helpful in preventing the device from going into deep CCM at VACMIN.

It should be noted that there are exceptions to the above, especially for very high output currents where the VOR should be depressed to get high efficiency, and higher output voltages above 15 V should be supported with higher VOR to maintain acceptable peak inverse voltage (PIV) across the output SR FET. Optimal selection of VOR depends on the specific application and should be based on a compromise between the factors described above.

#### Nominal Flyback Inductance, LP\_NOM

This is the target value for the nominal transformer primary inductance.

#### Flyback Inductance Tolerance, LP\_TOL

This parameter is the assumed tolerance for the transformer primary inductance. A value of 10% is used by default, a different value may be entered in the grey override cell. While a value of 10% is easy to meet a lower value will reduce production challenges.

#### Flyback Transformer Core Type, CR\_TYPE

By default, the spreadsheet will select the smallest commonly available core suitable for the specified output power. Different core types and sizes may be chosen from the drop-down list. If the user preferred core is not available, the grey override cells (AE, LE, AL, VE, AW and BW) can be used to enter the core and bobbin parameters directly.

|                    |        |             |       | Core | and Bobbin T | able  |          |        |       |

|--------------------|--------|-------------|-------|------|--------------|-------|----------|--------|-------|

|                    |        |             | Cor   | e    |              |       |          | Bobbin |       |

| Output<br>Power at | Carra  | Cada        | AE    | LE   | AL           | VE    | Cada     | AW     | BW    |

| 75 kHz             | Core   | Code        | (mm²) | (mm) | (nH/T²)      | (mm³) | Code     | (mm²)  | (mm)  |

| 0 W - 10 W         | EE10   | PC47EE10-Z  | 12.1  | 26.1 | 850          | 300   | B-EE10-H | 12.21  | 6.60  |

| 0 W - 10 W         | EE13   | PC47EE13-Z  | 17.1  | 30.2 | 1130         | 517   | B-EE13-H | 18.43  | 7.60  |

| 0 W - 10 W         | EE16   | PC47EE16-Z  | 19.2  | 35.0 | 1140         | 795   | B-EE16-H | 14.76  | 8.50  |

| 0 W - 10 W         | EE19   | PC47EE19-Z  | 23.0  | 39.4 | 1250         | 954   | B-EE19-H | 29.04  | 8.80  |

| 10 W – 20 W        | EE22   | PC47EE22-Z  | 41.0  | 39.4 | 1610         | 1620  | B-EE22-H | 19.44  | 8.45  |

| 10 W – 20 W        | EE25   | PC47EE25-Z  | 41.0  | 47.0 | 2140         | 1962  | B-EE25-H | 62.40  | 11.60 |

| 20 W – 50 W        | EE30   | PC47EE30-Z  | 111.0 | 58.0 | 4690         | 6290  | B-EE30-H | 41.79  | 13.20 |

| 0 W - 10 W         | RM5    | PC95RM05Z   | 24.8  | 23.2 | 2000         | 574   | B-RM05-V | 10.17  | 4.90  |

| 10 W – 20 W        | RM6    | PC95RM06Z   | 37.0  | 29.2 | 2150         | 1090  | B-RM06-V | 15.52  | 6.20  |

| 20 W – 30 W        | RM8    | PC95RM08Z   | 64.0  | 38.0 | 5290         | 2430  | B-RM08-V | 30.00  | 8.80  |

| 30 W – 50 W        | RM10   | PC95RM10Z   | 96.6  | 44.6 | 4050         | 4310  | B-RM10-V | 45.69  | 10.00 |

| 20 W – 30 W        | PQ2020 | PQ20/20-3F3 | 62.6  | 45.7 | 2650         | 2850  | P-2036   | 36.0   | 12.0  |

| 30 W – 50 W        | PQ2620 | PQ26/20-3F3 | 121.0 | 45.0 | 5200         | 5470  | BPQ26/20 | 31.1   | 9.0   |

Table 6. Commonly Available Cores and Associated Power Ranges Supported for Typical Flyback Transformer Designs.

# Safety Margin, MARGIN (mm)

By default, the safety margin is set to 0 which assumes that triple insulated wire will be used for secondary windings. If triple insulated wire is not used, then enter 3.1 for 230 VAC or universal input designs and 1.5 for low-line input (only) designs.

#### **Flyback Primary Turns, NP**

This is the number of turns for the main winding of the transformer calculated based on VOR and Secondary Turns NS.

#### Peak Flux Density, BP

A maximum value of 3600 gauss is recommended to limit the peak flux density at maximum current limit and 132 kHz operation. During an output short, the output voltage is low and little reset of the transformer occurs during the MOSFET off-time. This allows the transformer flux density to staircase, and rise above the normal operating limit, however a value of 3600 gauss at the maximum current limit of the selected device, together with the built-in protection features of LYTSwitch-6 ICs provides sufficient margin to prevent core saturation under these short-circuit conditions.

### Maximum Flux Density, B<sub>MAX</sub> (Gauss)

The low frequency operation resulting from light load can generate audible frequency components which will be amplified by the structure of the transformer, especially if a long core is used. To limit audible noise generation, the transformer should be designed such that the maximum core flux density is below 3000 gauss in normal operation. Following this guideline and using the standard transformer production technique of dip-varnishing practically eliminates audible noise, but optimization of audible noise should be undertaken using simple production transformer alternatives before finalizing the design.

#### AC Flux Density, BAC (Gauss)

The BAC value can be used for core loss calculation.

#### Gapped Core Effective Inductance, ALG (nH/N<sup>2</sup>) Used to specify the core gap.

#### Flyback Primary Layers, L

The number of primary layers should be between 1 and 3 and should meet the current capacity guideline of 200 - 500 circular mils/A in designs without forced air cooling. Values above 3 layers are possible but the increased leakage inductance as well as physical fit should be considered.

#### Primary Winding Wire Gauge, AWG

If the override cell is left blank, then the spreadsheet will calculate the AWG wire size based on the specified number of primary layers L.

## **Primary Bias Turns, NB**

Determined by:

$$NB = Ceiling\left(NS \times \frac{VBIAS}{VO}\right)$$

#### Secondary Turns, N<sub>s</sub>

By default, the minimum number of secondary turns is calculated such that the peak operating flux density BP is kept below the recommended maximum of 3600 gauss. Generally, it is not necessary to enter a number in the override cell except in designs where a lower operating flux density is desired.

# Step 8 – Primary Components Selection

Enter: Brown-In Voltage, V<sub>BIAS</sub>, VF <sub>BIAS</sub>, Zener Clamp

| 1   | ACDC_Flyback_PF_LYTSwitch-<br>6_040618; Rev. 1.3; Copyright Power<br>Integrations 2018 | INPUT | INFO | OUTPUT  | UNITS | Switched Valley-Fill Single Stage PFC (SVF<br>S^2PFC) |

|-----|----------------------------------------------------------------------------------------|-------|------|---------|-------|-------------------------------------------------------|

| 114 | Primary Components Selection                                                           |       |      |         |       |                                                       |

| 115 | Line Undervoltage                                                                      |       |      |         |       |                                                       |

| 116 | BROWN_IN_REQUIRED                                                                      | 70.00 |      | 70.00   | V     | Required AC RMS line voltage brown-in threshold       |

| 117 | RLS                                                                                    |       |      | 1.74    | MOhm  | Two Resistors of this Value in Series to the V-pin    |

| 118 | BROWN_IN_ACTUAL                                                                        |       |      | 69.80   | V     | Actual AC RMS brown-in threshold                      |

| 119 | Line Overvoltage                                                                       |       |      |         |       |                                                       |

| 120 | OVERVOLTAGE_LINE                                                                       |       |      | 290.83  | V     | Actual AC RMS line over-voltage threshold             |

| 121 | Bias Voltage                                                                           |       |      |         |       |                                                       |

| 122 | VBIAS                                                                                  |       |      | 12.00   | V     | Rectified Bias Voltage                                |

| 123 | VF_BIASDIODE                                                                           |       |      | 0.70    | V     | Bias Winding Diode Forward Drop                       |

| 124 | VRRM_BIASDIODE                                                                         |       |      | 62.64   | V     | Bias diode reverse voltage                            |

| 125 | CBIAS                                                                                  |       |      | 22.00   | μF    | Bias winding rectification capacitor                  |

| 126 | СВРР                                                                                   |       |      | 4.70    | μF    | BPP pin capacitor                                     |

| 127 | Bulk Capacitor Zener Clamp                                                             |       |      |         |       |                                                       |

| 128 | Use Clamp                                                                              | Yes   |      | Yes     |       | Bulk Capacitor Clamp Needed? Yes, No or N/A           |

| 129 | VZ1_V                                                                                  |       |      | 200.00  | V     | Zener 1 Voltage Rating (In Series with Zener 2)       |

| 130 | PZ1_W                                                                                  |       |      | 1.25    | W     | Zener 1 Minimum Power Rating                          |

| 131 | VZ2_V                                                                                  |       |      | 200.00  | V     | Zener 2 Voltage Rating                                |

| 132 | PZ2_W                                                                                  |       |      | 1.25    | W     | Zener 2 Minimum Power Rating                          |

| 133 | RZ                                                                                     |       |      | 4700.00 | Ohm   | Resistor in series with Zener 1 and Zener 2           |

Figure 16. Primary Components Selection Section of the Design Spreadsheet.

#### Brown-in Voltage, BROWN\_IN\_REQUIRED (V)

This is the input AC voltage at which the power supply will turn on once the brown-in threshold  $(\rm I_{\rm UV+})$  is exceeded.

#### Line Sense Resistor, RLS (M $\Omega$ )

Line sense resistor RLS sets the brown-in voltage and line overvoltage thresholds. It is typically shown as two resistors in series RLS1 and RLS2 and is connected to the bulk capacitor.

$$RLS = \frac{V_{BROWN\_IN\_REQUIRED} \times \sqrt{2}}{I_{UV+}}$$

#### Line Overvoltage, OVERVOLTAGE\_LINE (V)

This is the input AC voltage at which the power supply will stop switching as soon as the overvoltage threshold  $(I_{\rm ov})$  is exceeded. Switching is re-enabled when the line overvoltage hysteresis  $(I_{\rm ov(H)})$  is reached.

$$OVERVOLTAGE\_LINE = \frac{I_{ov-} \times RLS}{\sqrt{2}}$$

#### Rectified Bias Voltage, VBIAS (V)

A default value of 12 V is assumed. The voltage may be set to different values, for example when the bias winding output is also used as a primary-side (non-isolated) auxiliary output. Higher voltages typically increase no-load power consumption. Values below 10 V are not recommended since at light load there may be insufficient voltage to supply current to the PRIMARY BYPASS pin which could lead to a significant increase in no-load input power consumption.

#### Bias Diode Forward Drop, VF\_BIASDIODE (V)

A default value of 0.7 V is used. This should be changed depending on the type of diode used for bias winding rectification.

#### BPP Pin Capacitor, CBPP (µF)

CBPP determines the ILIMIT\_MODE of operation for the device. Use 0.47  $\mu$ F for STANDARD current limit and 4.7  $\mu$ F for INCREASED current limit. The capacitor can either be an electrolytic or a ceramic type. Surface mount multi-layer ceramic capacitors are preferred for use with double-sided boards as they enable the capacitors to be placed close to the IC. Ceramic X7R (or better) capacitors of at least 25 V voltage rating are recommended.

#### Primary Bias Supply Components (CBIAS, DBIAS, RBP)

While the PRIMARY BYPASS pin has an internal regulator that charges the PRIMARY BYPASS pin capacitor to  $V_{\rm BPP}$  by drawing current from the voltage on the DRAIN pin whenever the power MOSFET is off, an external bias supply via an additional primary auxiliary winding is commonly employed. This will reduce the no-load power consumption of the IC.

A 22  $\mu$ F, 50 V, low ESR electrolytic aluminum capacitor is recommended for the bias supply filter, CBIAS. The use of a low ESR electrolytic capacitor is recommended as it reduces no-load input power. Use of ceramic surface mount capacitor is not recommended as this can cause audible noise due to a piezoelectric effect from the capacitor's mechanical structure.

The bias winding rectifier diode DBIAS can either be a standard recovery or a fast recovery type. The former tends to give lower radiated EMI while the latter results to lower no-load input power.

The resistor RBP is selected to ensure that the current supplied by the primary bias supply is higher than the PRIMARY BYPASS pin supply current  $\rm I_{ssw}$ .  $\rm I_{ssw}$  is calculated as follows:

$$I_{SSW} = \frac{F_{SW}}{132 \, kHz} \times (I_{S2} - I_{S1}) + I_{S1}$$

Where:

- ${\rm I}_{\rm ssw}$ : PRIMARY BYPASS pin supply current at operating switching frequency.

- $\rm F_{\rm sw}$  . Operating switching frequency (kHz) the average between FSMIN and FSMAX.

- $I_{s_1}$ : Non-switching PRIMARY BYPASS pin current (refer to data sheet).

- $I_{s_2}^{3}$ : PRIMARY BYPASS pin supply current at 132 kHz (refer to data sheet).

The BPP voltage will be ~5.3 V if bias current is higher than PRIMARY BYPASS pin supply current. If BPP voltage is ~5.0 V, this indicates that the current through RBP is less than the required PRIMARY BYPASS pin supply current. Ensure that the voltage at the PRIMARY BYPASS pin never falls below 5.0 V except during start-up.

RBP is determined by:

$$RBP = \left(\frac{VBIAS_{NO-LOAD} - 5.3V}{I_{SSW}}\right)$$

### **Bulk Capacitor Zener Clamp Selection**

When set to yes, the spreadsheet will calculate the Zener voltage rating (VZ1\_V, VZ2\_V), the power rating (PZ1\_W, PZ2\_W), and the series resistor RZ.

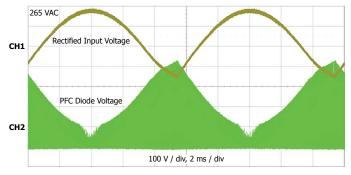

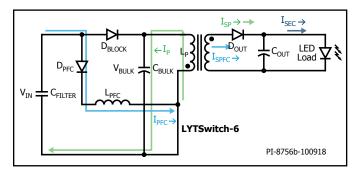

#### PFC Diodes, DBOOST1 and DBOOST2

The PFC diodes (DBOOST1, DBOOST2), placed in series with the PFC inductor LBOOST, provide a current path for the energy stored in the PFC inductor that must be transferred to the secondary-side during the MOSFET off-time. However, the resonant voltage ring from the PFC inductor when the MOSFET turns off will cause a large voltage ring across the PFC diode. Select the PFC diode based on the following:

- For high-line / universal input, use 2 x 600 V, ultrafast-recovery diodes in series.

- For low-line input, use 1 x 600 V, ultrafast-recovery diode.

- A current rating of 1 A is sufficient in most applications but a higher rating may be used to reduce device temperature if necessary.

Figure 17. Voltage Stress across the PFC Diode.

### Blocking Diode to the Bulk Capacitor, DBLOCK

The blocking diode DBLOCK isolates the rectified AC input from the bulk capacitor. It provides current path for charging the bulk capacitor which improves efficiency especially at low-line.

A standard recovery diode with a voltage rating of 600 V and current rating of 1 A is recommended.

# Step 9 – Secondary Controller Components Selection

| 1   | ACDC_Flyback_PF_LYTSwitch-<br>6_040618; Rev.1.3; Copyright Power<br>Integrations 2018 | INPUT | INFO | ΟυΤΡυΤ | UNITS | Switched Valley-Fill Single Stage PFC (SVF<br>S^2PFC)               |

|-----|---------------------------------------------------------------------------------------|-------|------|--------|-------|---------------------------------------------------------------------|

| 134 | Secondary Components Selection                                                        |       |      |        |       |                                                                     |

| 135 | IS pin Components                                                                     |       |      |        |       |                                                                     |

| 136 | R_ISpin                                                                               |       |      | 33.60  | mOhm  | Non Standard Value of IS pin 1% resistor                            |

| 137 | Feedback Components                                                                   |       |      |        |       |                                                                     |

| 138 | RFB_UPPER                                                                             |       |      | 102.00 | kOhm  | Upper feedback 1% resistor                                          |

| 139 | RFB_LOWER                                                                             |       |      | 3.30   | kOhm  | Lower feedback 1% resistor                                          |

| 140 | CFB_LOWER                                                                             |       |      | 330.00 | pF    | Lower feedback resistor decoupling at least 5V-<br>rating capacitor |

| 141 | CBPS                                                                                  |       |      | 2.20   | μF    | BPS pin capacitor                                                   |

Figure 18. Secondary Components Selection from the Design Spreadsheet.

### Current Sense Resistor, RIS (m $\Omega$ )

The external current sense resistor, R\_ISPIN, sets the constant current (CC) threshold. In the spreadsheet, it is assumed that the specified output current IO is also the CC threshold. The current sense resistor value is therefore calculated as;

$$R\_ISPIN = \frac{I_{SV(TH)}}{IO}; I_{SV(TH)} = 35.9 mV$$

#### **Current Sense Protection Diode, DIS**

This diode is connected across the current sense resistor to protect the device during output short-circuit.

# Upper Feedback Resistor, RFB\_UPPER (kΩ)

The mid-point of an external resistor divider network (RFB\_UPPER, RFB\_LOWER) connected between the OUTPUT VOLTAGE and SECONDARY GROUND pins is tied to the FEEDBACK pin to regulate output voltage. The internal voltage comparator reference voltage is  $V_{\rm REF}$  (1.265 V).

The default value for RFB\_UPPER is 102 k $\Omega$ . However, for applications that have stringent no-load input power requirements, this value may be adjusted to reduce no-load consumption especially if the rated output voltage is above 20 V.

## Lower Feedback Resistor, RFB\_LOWER (k $\Omega$ )

The RFB\_LOWER resistor is calculated using the RFB\_UPPER value.

# Lower Feedback Resistor Decoupling Capacitor, CFB\_LOWER (pF)

A 330 pF, surface-mount, X7R ceramic capacitor, connected close to the FEEDBACK and GROUND pins of the IC, is recommended.

#### Secondary Bypass Pin Capacitor, CBPS (µF)

This capacitor works as a voltage supply decoupling capacitor for the integrated secondary-side controller. A surface-mount, 2.2  $\mu$ F, 25 V, X5R or X7R, ceramic capacitor is recommended.

#### Forward Pin Resistor, RFWD (Ω)

The FORWARD pin is connected to the Drain terminal of the synchronous rectifier FET (SR FET). This pin is used to sense the Drain voltage of the SR FET and precisely turn-on and turn-off the device. It is also used to provide charge to the SECONDARY BYPASS pin capacitor (CBPS) whenever the output voltage falls below the SECONDARY BYPASS pin voltage.

A 47  $\Omega$ , 5% resistor is recommended to ensure sufficient IC supply current and works across a very wide range of output voltages. Changing this value may adversely effect the timing of the synchronous rectifier drive. Care should be taken to ensure that the voltage on the FORWARD pin never exceeds its absolute maximum voltage. If the FORWARD pin voltage exceeds the FORWARD pin absolute maximum voltage (see data sheet), the IC will be damaged.

If secondary auxiliary winding is used, such as when the output voltage is >24 V, then the FORWARD pin is typically connected to the auxiliary winding through RFWD.

Enter: VAUX, VF\_AUX, CAUX

| 1   | ACDC_Flyback_PF_LYTSwitch-<br>6_040618; Rev.1.3; Copyright Power<br>Integrations 2018 | INPUT | INFO | Ουτρυτ | UNITS | Switched Valley-Fill Single Stage PFC (SVF<br>S^2PFC) |

|-----|---------------------------------------------------------------------------------------|-------|------|--------|-------|-------------------------------------------------------|

| 142 | Secondary Auxiliary Section - For VO > 24V ONLY                                       |       |      |        |       |                                                       |

| 143 | Sec Aux Diode                                                                         |       |      |        |       |                                                       |

| 144 | VAUX                                                                                  |       |      | 12.00  | V     | Rectified auxiliary voltage                           |

| 145 | VF_AUX                                                                                |       |      | 0.70   | V     | Auxiliary winding diode forward drop                  |

| 146 | VRRM_AUXDIODE                                                                         |       |      | 62.64  | V     | Auxiliary diode reverse voltage                       |

| 147 | CAUX                                                                                  |       |      | 22.00  | μF    | Auxiliary winding rectification capacitor             |

| 148 | NAUX_SEC                                                                              |       |      | 5.00   |       | Secondary Aux Turns                                   |

| 149 | AWGSAUX                                                                               |       |      | 32     |       | Secondary Aux Winding AWG                             |

Figure 19. Secondary Auxiliary Section of the Design Spreadsheet.

#### Secondary Auxiliary Voltage, VAUX (V)

The OUTPUT VOLTAGE (VOUT) pin has a maximum voltage rating of 27 V. For designs with higher than 24 V output voltage requirements, adding an auxiliary winding for VOUT and FWD pin sensing is recommended.

By default, the secondary auxiliary voltage is set to 12 V.

# Auxiliary Diode Forward Drop, VF\_AUX (V)

A default value of 0.7 V is used but should be changed on the type of diode used for auxiliary winding rectification.

#### Auxiliary Rectifier Reverse Voltage, VRRM\_AUXDIODE (V)

This parameter is the maximum voltage stress on the secondary rectifier at the maximum input voltage – neglecting the effect of leakage spikes.

#### Secondary Bias Supply Components (CAUX, DAUX)

A 22  $\mu$ F, 50 V, low ESR electrolytic aluminum capacitor is recommended for the secondary auxiliary supply filter, CAUX.

The secondary auxiliary winding rectifier diode, DAUX, should be a standard recovery type with a voltage rating of 200 V. While the calculated VRRM\_AUXDIODE may be low, the leakage spike may exceed 100 V in conditions such as cold start-up. It should not exceed 150 V which is the FORWARD (FWD) pin maximum voltage rating. Even a short pulse exceeding this value may cause damage to the IC. The R-C snubber on the main output rectifier is usually sufficient to prevent this. Adding an R-C snubber across DAUX is optional, but it should be considered if the leakage spike approaches the 150 V limit.

# Step 11 – Output Rectifier and Capacitor Selection

| 1   | ACDC_Flyback_PF_LYTSwitch-<br>6_040618; Rev.1.3; Copyright Power<br>Integrations 2018 | INPUT | INFO | OUTPUT | UNITS | Switched Valley-Fill Single Stage PFC (SVF<br>S^2PFC) |

|-----|---------------------------------------------------------------------------------------|-------|------|--------|-------|-------------------------------------------------------|

| 154 | Output Components                                                                     |       |      |        |       |                                                       |

| 155 | VF                                                                                    |       |      | 0.70   | V     | Output diode forward drop                             |

| 156 | VRRM                                                                                  |       |      | 191.93 | V     | Output diode reverse voltage                          |

| 157 | COUT                                                                                  |       |      | 222.22 | μF    | Output Capacitor - Capacitance                        |

| 158 | COUT_VOpercentRip                                                                     |       |      | 2.50   | %     | Output Capacitor Ripple % of VOUT                     |

| 159 | ICOUTrms                                                                              |       |      | 1.37   | A     | Output Capacitor Estimated Ripple Current             |

| 160 | ESRmax                                                                                |       |      | 232.28 | mOhm  | Output Capacitor Maximum Recommended ESR              |

Figure 20. Output Rectifier and Capacitor Section of the Design Spreadsheet.

### **Output Rectifier Forward Drop, VF (V)**

A default value of 0.7 V is used but should be changed to a different type of diode used for rectification of the secondary main output winding.

#### Output Rectifier Reverse Voltage, VRRM (V)

This parameter is the maximum voltage stress on the secondary rectifier at the maximum input voltage neglecting the effect of leakage spikes. Extra margin must be provided when choosing the voltage rating of the device to account for leakage spikes.

$$VRRM = VOUT + VACMAX \times 1.414 \times \frac{NS}{NP}$$

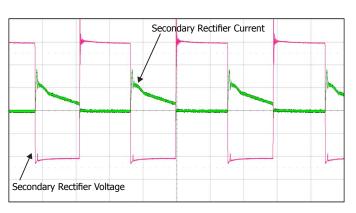

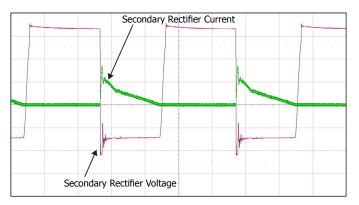

#### **Output Rectifier, DOUT**

Use synchronous rectifier FET (SR FET) whenever possible to get highest efficiency. The SR pin drive voltage has a typical value of 4.4 V. A gate threshold voltage of 1.5 V – 2.5 V is ideal when choosing the SR FET. MOSFETs with a threshold voltage as high as 4 V may be used provided that the data sheet specified  $R_{DS(ON)}$  across temperature for a gate voltage of 4.5 V.

For a high output voltage design with a calculated VRRM of >150 V, the SYNCHRONOUS RECTIFIER DRIVE pin needs to be connected to the SECONDARY GROUND pin to allow the use of a low-cost ultrafast diode instead of an SR FET.

### Output Rectifier Snubber, RSR (Ω), CSR (nF)

The interaction between the leakage reactance of the output winding and the output capacitance ( $C_{oss}$ ) of the output rectifier leads to voltage ringing at the instant of winding voltage reversal when the primary MOSFET turns on. This ringing can be suppressed using an RC snubber connected across the output rectifier. A snubber resistor in the range of 10  $\Omega$  to 47  $\Omega$  should be used (higher resistance values lead to a noticeable drop in efficiency). A capacitor value of 1 nF to 2.2 nF is adequate for most designs.

#### Target Output Voltage Ripple for Capacitor Sizing, COUT\_VOpercentRip (%)

This parameter sets the target output voltage ripple percentage which is used to calculate the minimum output capacitance.

#### Output Capacitance, COUT (µF)

The minimum recommended output capacitance, COUT, is calculated based on the target voltage ripple COUT\_VOpercentRip. Higher capacitance may be used if lower output current ripple is required. Verification with an actual LED load is needed. Different LED strings have different dynamic impedance characteristics which determine the actual ripple current. A low ESR type capacitor is typically used to reduce output voltage ripple.

## Step 12 – Other Key Components Selection

#### Primary Clamp Network (DSN, RS, RSN, and CSN)

A primary clamp is recommended to ensure that the  $\mathsf{BV}_{\mathsf{DSS}}$  rating of the IC is not exceeded under worst-case conditions (such as output short-circuit at maximum input voltage).

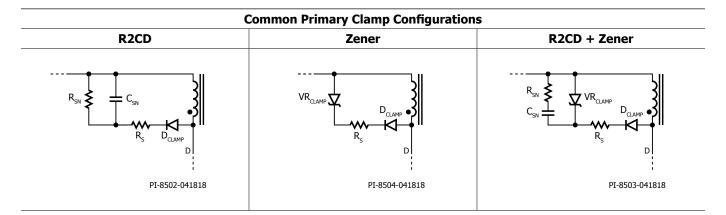

Figure 21 shows three common clamp configurations in the design. Table 7 lists the benefits and disadvantages of each circuit approach.

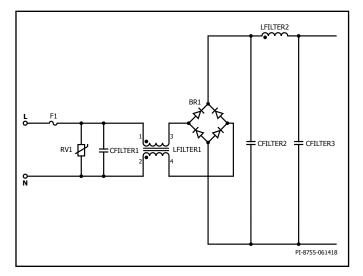

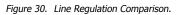

#### **Input Filter and Protection**

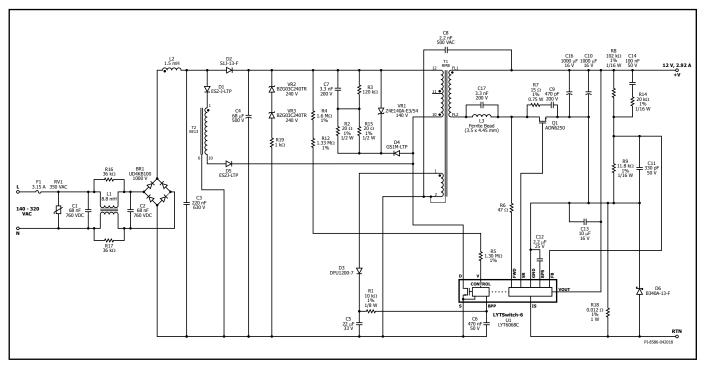

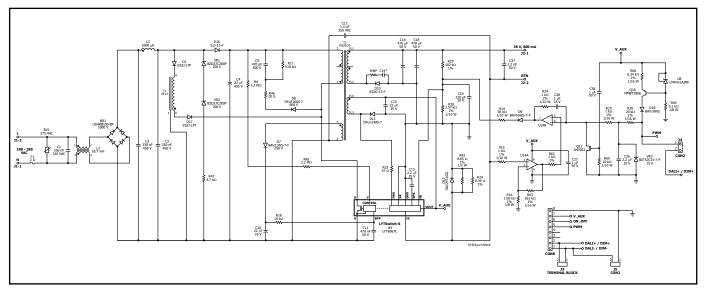

Figure 22 shows the typical input protection components and EMI filter component arrangements used in a typical LYTSwitch-6 design.

Fuse F1 provides over-current protection and isolates the power supply from the AC line in case of catastrophic failure. A time-lag fuse is commonly used to prevent tripping during start-up due to high inrush current from the charging of the bulk capacitor. Use 250 VAC rating for a 230 / 240 VAC input system and 300 VAC rating for a

Figure 21. Recommended Primary Clamp Components.

| Primary Clamp Circuit |      |        |              |  |  |  |  |

|-----------------------|------|--------|--------------|--|--|--|--|

| Benefits              | R2CD | Zener  | R2CD + Zener |  |  |  |  |

| Component Cost        | Low  | Medium | High         |  |  |  |  |

| No-Load Input Power   | High | Low    | Medium       |  |  |  |  |

| Light-Load Efficiency | Low  | High   | Medium       |  |  |  |  |

| EMI Suppression       | High | Low    | Medium       |  |  |  |  |

Table 7. Benefits of Primary Clamp Circuits.

Figure 22. Input Filter Configuration in LYTSwitch-6 Designs.

277 VAC input system. The rated current should be greater than the maximum current at minimum input voltage. Ensure that the  $I^2 t$  rating is greater than the  $I^2 t$  measured during inrush and surge events.

Bridge rectifier BR1 rectifies the AC line. The voltage rating of the bridge is recommended to be 1 kV especially if 2.5 kV ring-wave immunity is required. The current rating should be greater than the maximum operating current. Choose the appropriate package size based on power dissipation and thermal measurements.